所有的媒体都正在向数字格式进行转换,现在就连音乐也几乎都是数字的。电视和视频正迅速转换为全数字格式。数码照片将很快淘汰过时的胶卷。在今后几年,这种转换将是全方位的,数字媒体格式将会成为标准格式。因此,电子行业需要面临数字媒体格式转换引擎的开发,以此为媒体用户提供声音和图像。

音频技术作为第一种完全数字化的媒体,在转换方面进行得最为深入。现在的音频系统必须支持多种数字音频格式,从最早的格式到最新的格式。随着数字音频格式变得越来越先进,其技术也越来越复杂,目的是通过使用更少的位数来得到更好的声音效果。随着大量的数字音频媒体格式(包括MP3、AC3、AAC和WMA)和用于手机的各种语音编解码器的使用,数字音频格式的转换需要某种固件可编程的处理器。对于诸多不同数字音频格式的转换而言,采用专用硬件会显得过于复杂。

许多种可编程处理器都可以用于数字音频格式的转换处理。对PC而言,一般采用通用的32位或者64位CPU处理音频数据,因为这在PC中已经很普遍。这些CPU的主频现在已经达到几GHz,因此其带宽足可以轻松地处理音频数据格式的转换,然而其成本也高达数百美元,且功耗达到几十上百瓦,因此,通用CPU并不适合低功耗、以电池作为电源的设备。

低功耗、低成本的数字信号处理器(DSP)也可以在许多消费类设备中用于实现数字音频编解码器。一般而言,低成本DSP为16位DSP,这类处理器在正确处理现在复杂的16位音频数据编解码时缺少足够的位精度,更不用说更加先进的20位音频格式了。而且,DSP一般缺少媒体产品中与任务控制相关的指令和输入/输出功能,因此在这类设计中通常需要一个控制处理器。这样做的后果是,即使是一个简单的基于DSP的音频播放器也必须要采用双处理器体系结构,这使得设计变得复杂,并增加了设计中存在缺陷的风险。

采用可配置处理器内核可以构建一个音频处理器,该处理器既具有DSP的高性能与低功耗特性,又具有通用处理器的良好控制能力。Tensilica的基于Xtensa的HiFi音频引擎即是该类处理器的范例。HiFi音频处理器基于32位的Xtensa V处理器内核,具有24位音频专用的指令。该处理器内核已经在多种产品中采用,包括移动电话、便携式音频播放器、便携摄像机、数码相机以及个人视频录像(PVR)。

Tensilica公司Xtensa LX可配置处理器的推出可以提高原有的HiFi音频引擎性能,为用户提供被称为Xtensa HiFi 2音频引擎的更加强大的音频处理器。该引擎可以利用更窄的带宽(因而功耗和能量更低)来运行更复杂的数字音频编解码算法。Xtensa LX处理器具有某些可配置特性,因而可以允许上述的这些改进。

特别的是,Xtensa LX处理器具有称为FLIX(可变长度指令扩展)的功能,允许处理器将现有的16位和24位Xtensa指令混和生成定制的宽指令。每一条FLIX格式的指令都可以将多个独立的操作放进每个宽指令字中的操作槽中。Xtensa LX处理器的Xtensa HiFi 2音频引擎扩展就增加了300多条专用音频DSP指令,包括24位的MAC(乘法/累加)指令和流编码指令,这些指令的引入大大减少了复杂音频编解码算法的执行周期数。

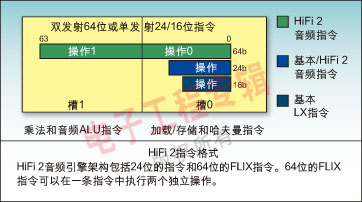

有些新的专用音频指令为24位指令,有些则为64位FLIX格式的指令。HiFi 2音频引擎的FLIX格式指令包括两个操作槽。所有的HiFi 2音频引擎指令扩展都可以直接利用与Tensilica的自动化Xtensa Processor Generator(处理器生成器)生成的处理器一起产生的编译器。如图1所示。

图1:HiFi 2指令格式

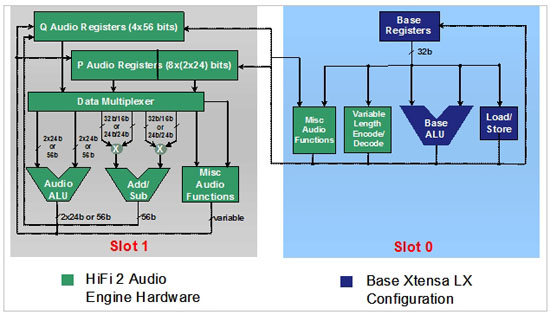

HiFi 2音频引擎扩展对Xtensa LX处理器增加的硬件包括两个MAC单元。每个MAC单元可以执行24×24位和32×16位的乘法,两个MAC单元都采用流水线方式执行,因此每个时钟周期都可以产生一个新的执行结果。增加的硬件还包括哈夫曼编码器和解码器、一个位流处理器和两个用于处理24位音频数据的专用寄存器文件。其中一个寄存器文件包括8个48位寄存器,每个寄存器可以存放两个24位数据值;另一个寄存器文件包括4个56位寄存器,保存两个MAC单元产生的扩展精度运算结果。如图2所示。

移植到Xtensa HiFi 2音频引擎结构的数字音频编解码算法的性能结果表明,设计只需要很小的处理器带宽就可以支持高质量的音频编解码。例如,MP3解码器在播放以48kHz/128kbps立体声格式存储的音乐时,只需要13~15MHz的处理器带宽。而在类似的码率下,MP3编码器也只需38~40MHz的处理器带宽。AAC-LC编码器/解码器以及WMA解码器也可以获得相似的结果。

Xtensa LX处理器采用广泛的时钟门控技术,该技术超越了Xtensa V处理器设计中使用的该技术,以用来降低功耗。该特性以及用来在Xtensa HiFi2音频引擎架构上实现数字音频编解码所需的低时钟速率一起,产生了非常高效的音频处理器。具有Xtensa HiFi 2音频引擎扩展的Xtensa LX处理器采用TSMC 的130nm LV制造工艺,功耗只有91μW/MHz;而原来基于Xtensa V处理器的HiFi音频引擎的功耗则为207μW/MHz。

当执行AAC-LC编码器算法时,HiFi 2音频引擎工作频率为38MHz;而原来的Xtensa HiFi音频引擎工作频率则为85MHz。这些改进的结果是,在执行AAC-LC编码器算法时,Xtensa HiFi 2音频引擎的功耗为3.5mW;而原来的Xtensa HiFi音频引擎在执行相同任务时功耗则为17.6mW。尽管原来的Xtensa HiFi音频引擎的功耗已经很低了,但是Xtensa HiFi 2音频引擎的功耗仍然比原来降低了五倍。

&nbs[FS:Page]p; Xtensa HiFi 2音频引擎架构同原来成功的Xtensa HiFi音频引擎相比,有三个方面的优势。首先,Xtensa HiFi 2音频引擎降低了实现先进的数字音频编解码的处理器带宽。其次,在执行这些数字音频编解码算法时,降低了功耗,这是由于需要的带宽降低,以及因为Xtensa HiFi 2所基于的Xtensa LX处理器与以前的Xtensa V处理器相比具有更多的扩展时钟门控。最后,基于Xtensa LX的Xtensa HiFi 2音频引擎架构与原来基于Xtensa V处理器的Xtensa HiFi引擎相比,实现时需要更少的门数(在200MHz时钟速率下,综合出来的处理器门数减少了大约20%)。

通过增加专用音频指令,Tensilica的Xtensa LX处理器可以提供一个高效的、低功耗、高性能平台用于构建数字音频产品。这样的平台可以执行多种音频编解码算法,同时如果需要的话也能执行超越传统DSP的控制类任务。而且,Xtensa HiFi 2音频引擎可以提供相同性能下低得多的成本和时钟频率。因此,与通用CPU相比可以大大降低功耗级别。

为您推荐

这种Amino新一代产品将满足不断增长的来自电视娱乐任何方面的消费需求,包括广播,点播和开放互联网OTT服务。采用全新的英特尔®Atom™处理器CE4100的Amino发展新型混合/OTT试验设备,提供无与伦比的灵活性和功能。该CE4100媒体处理器结合了领先的高清晰视频,支持家庭影院质量的音频前沿的CE功能和先进的3-D图形的性能,可以提供基于英特尔架构的灵活性和硬件和软件兼容性。该CE4100将使IPTV机顶盒提供一个全面开放的互联网的经验,从而为网络运营商和服务供应商提供新的机会,增强他们的客户娱乐体验。

随着移动电视、GPS、摄像、游戏和MP3等应用成为下一代多功能手机的基本配置,应用处理器开始取代基带处理器成为手机设计的核心部分,因此,对应用处理器的性能提出了更高的要求。针对手机设计的这一需求,国内厂商纷纷推出了高品质的产品。安凯微电子的AK88系列多媒体应用处理器采用ARM926EJ内核,集成了GPS加速器、MPEG2解码器、MPEG4-ASP解码器、H.264和RM解码器等,支持丰富的视频格式,如RM/RMVB、MPEG2、MPEG4SP/ASP、H.264、H.263等几乎所有常见的视频格式。除强大的视频播放能力以外,AK88系列还内置了丰富的接口和加速器,例如:AudioCodec、

2009年下半年展讯向市场推出6600L后,几乎一度抢过竞争对手MTK的6225市场。但在2009年10月之后,MTK被动格局上发生了变化。具体原因,还得从此次参展IIC-China的北京思比科微电子股份有限公司(以下思比科微电子)推出了一款协处理器SP5368说起。思比科微电子是一家总部在北京的IC设计公司,专门定位于视频处理技术,在CMOS图像传感器上推出了领先的产品。但由于产品定位过高当时并没有获得成功。公司副总裁赵文霖说,国内手机上采用的CMOS图像传感器市场主要是100万像素以下的低端产品,对于公司开发出来的200万像素以上的需求并没有起来。后来公司转为开发采用有视频硬解码的协

AnalogDevices,Inc.最新推出32位浮点数字信号处理器SHARC产品组合的最新成员--SHARC2148x及SHARC2147x系列。高性能SHARC2148x及低功耗SHARC2147x系列处理器凭借集成高达5Mb的存储器,为各种应用提高了单芯片、浮点信号处理精度,并为便携式设备实现了高端系统功能。通过SHARC2148x及SHARC2147x处理器,设计师可以利用端到端SHARC系列的代码兼容性及鲁棒的ADI开发工具套件,借助性能极佳的32位浮点DSP平台来实现更高水平的开发效率和设计创新。--SHARC2148x系列相比于以往为专用系统保留的用以容纳多处理器、片外存储器的电